Synthesis and P&R for the DIGITAL blocks of mixed-signal designs

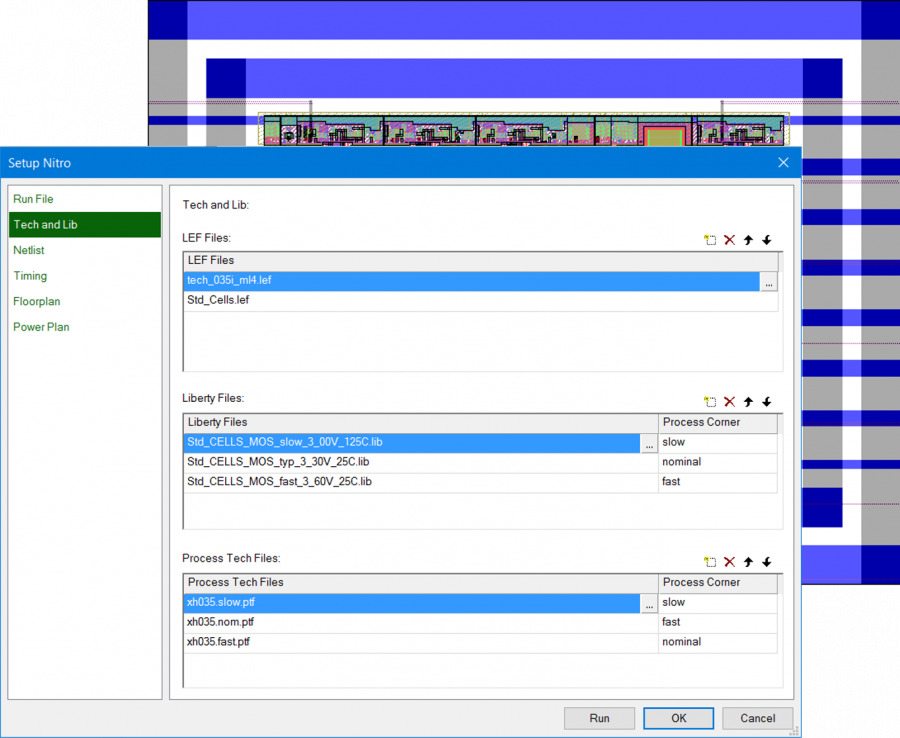

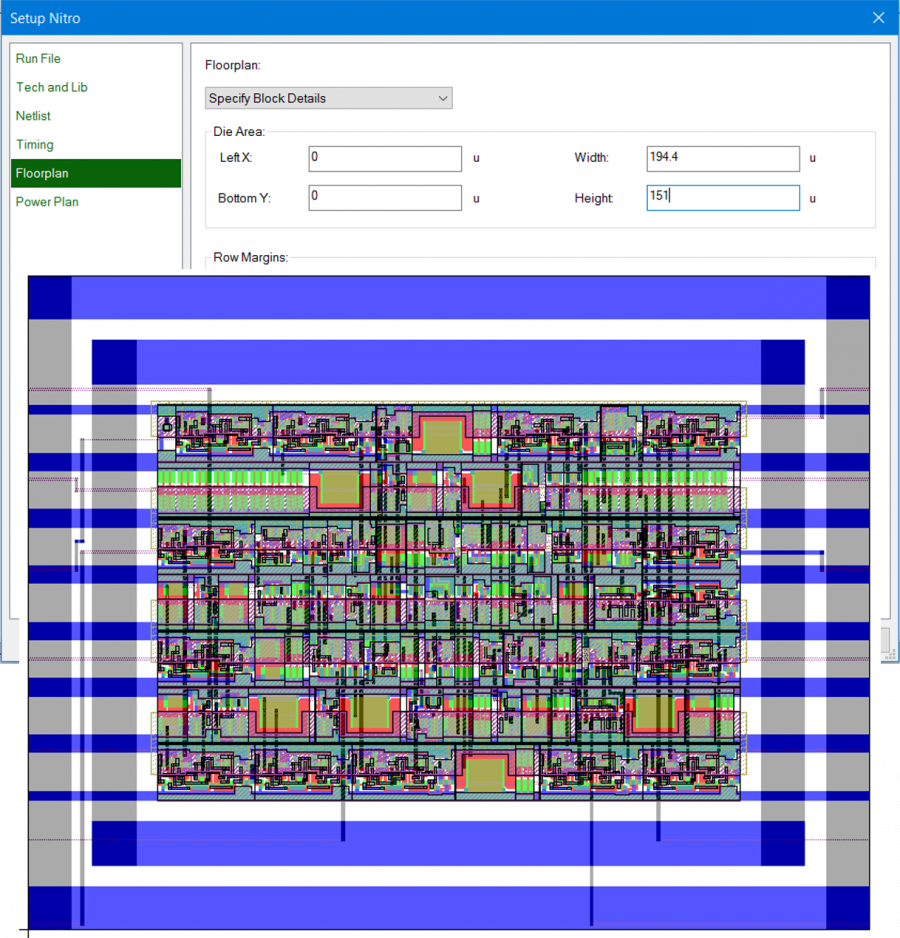

Tanner Digital Implementer (TDI) is built on an efficient synthesis and powerful P&R (place-and-route) engine. It is integrated into the L-Edit physical layout tool to address the physical implementation of the digital needs of “Analog on Top” designs. With analog designs increasingly digitally-assisted to enhance analog capabilities, such as automated calibration and programmability.

Tanner Digital Implementer is designed to augment a mixed-signal environment rather than be a go-to solution for full digital chips at sub-22nm FinFET nodes. The result is an effective, cost effective solution made efficient for the types of digital blocks More-than-Moore mixed-signal designers must implement.

- Timing driven P&R

- Supports low-power design methodologies

- Floor plan and power plan functionality